# Uma Arquitetura de Testes para Computadores de Bordo

#### Cláudia Santos da Silva

Orientadora: Eliane Martins

### Introdução

- Sistemas de Tempo Real

- Sistemas de Tempo Real Embarcados

- Característica Confiabilidade

- Investir no processo de desenvolvimento

- SUBORD (Supervisão de Bordo)

- Crescente evolução tecnológica

- Inviabilidade de um equipamento de testes para cada aplicação

# Objetivo

Adaptar uma arquitetura para teste de software para computadores de bordo.

### Estrutura da Apresentação

- Arquitetura Ferry Clip

- Projeto ATIFS

- Arquitetura utilizada no FBM que fará parte do estudo de caso

- Resultados esperados

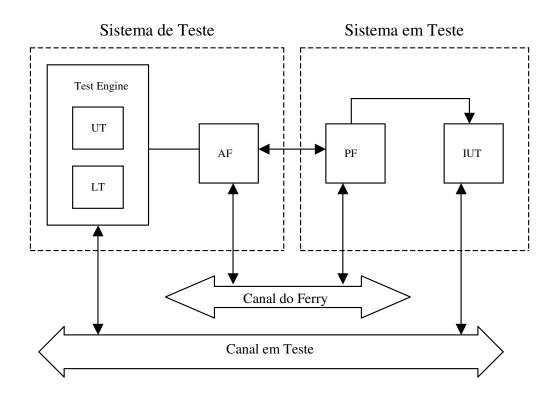

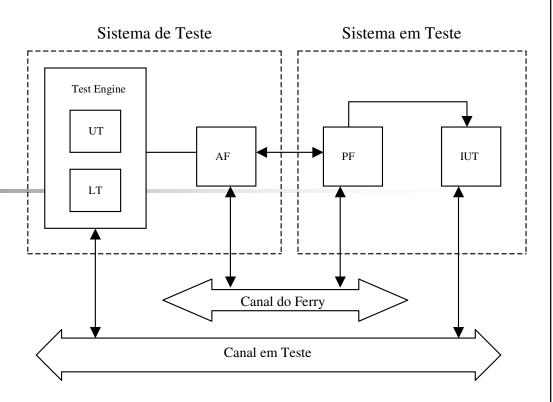

### Arquitetura Ferry clip

desenvolvida com o objetivo de dar suporte às metodologias de teste definidas pelo ISO

permitir que os dados sejam trocados entre o Sistema em Teste e o Sistema de Teste

# Motivos da escolha da arquitetura Ferry clip

- facilidade de portar para diferentes plataformas

- facilidade de adaptar a diferentes implementações

- facilidade no acréscimo de novas funcionalidades

- estudo que vem sendo feito desta arquitetura no Instituto da Computação (IC) na UNICAMP

### **Principais Componentes**

Ferry Ativo (AF): contém o software necessário para estabelecer, manter e trocar dados com o PF

Ferry Passivo (PF):possui um código para estabelecer e manter a conexão com o AF

### Arquitetura Ferry Clip

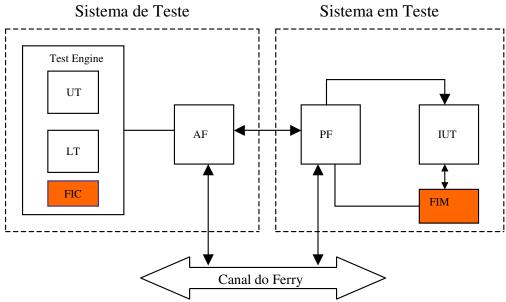

### **ATIFS**

dar suporte à realização de testes em protocolos de comunicação

- desenvolvida através da extensão da arquitetura Ferry Clip

- permitir a injeção lógica de falhas

# Arquitetura da FsoFIST

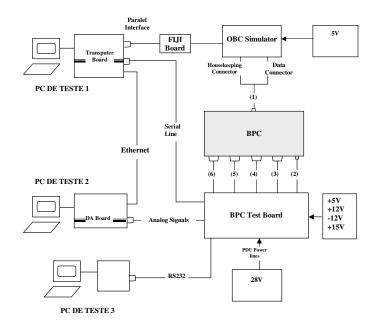

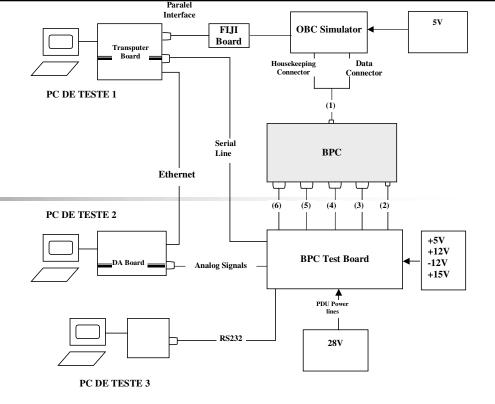

# Arquitetura do Equipamento de Testes do BPC

- responsável por prover os recursos necessários para desenvolvimento e testes do hardware e software do BPC

- O software do Equipamento de Testes está distribuído:

- PC de teste 1, que contém a placa de desenvolvimento do Transputer

- PC de Teste 2, que contém a placa AD/DA

- PC de Teste 3 e no Simulador do Equipamento denominado OBC

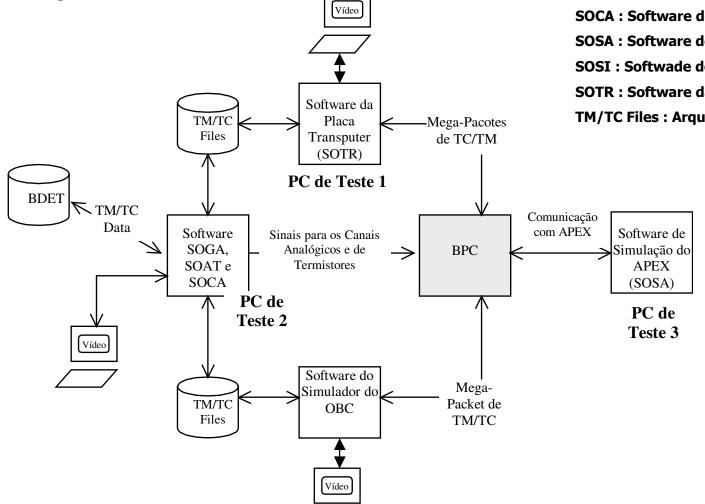

# Arquitetura do Equipamento de Testes do BPC

## Software do Equipamento de

**Testes**

**BDET : Banco de Dados do Equipamento de Testes**

**SOGA : Software para Geração de Pacotesde TM dos**

**Experimentos**

**SOAT : Software de Análise de Telemetria**

**SOCA: Software de Controle da Placa AD/DA**

**SOSA : Software de Simulação do APEX**

**SOSI: Softwade do Simulador do OBC**

**SOTR : Software da Placa do Transputer**

TM/TC Files: Arquivos com pacotes de TM e TC

# Resultados Esperados

- estender a arquitetura ferry clip para teste de software para computadores de bordo

- testes multi-ponto

- testes de interoperabilidade

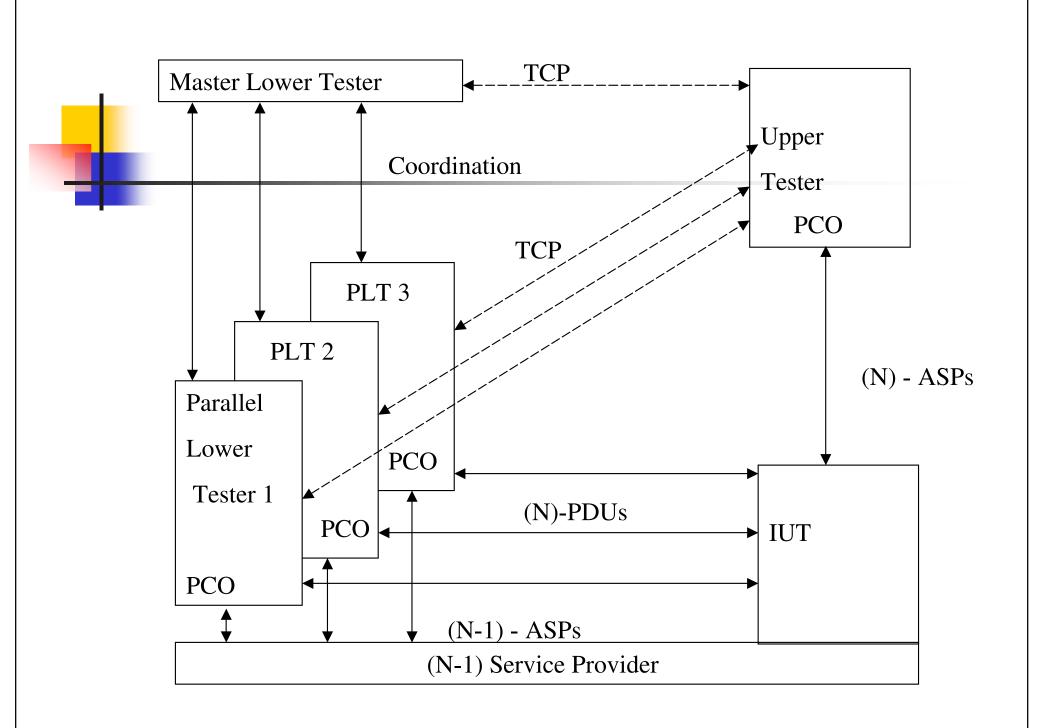

### Teste Multi-partes

- Pontos de Controle e Observação

- A capacidade da IUT manipular concorrência com mais de uma conexão

- Sincronização

- Configuração dos Testadores e da IUT